# Sync Box User's Guide

## Revision History:

Rev. 1.b RJ July 07, 2006 Draft

Rev. 1.c RJ Oct. 25, 2006

Rev. 1.d RJ Dec. 8, 2006 updated block diagram

Rev. 1.1 MA Jun. 7, 2007 added document number and revision history

(For SyncoCmd-V1c and firmware SC2-SyncBox-6c)

# **Table of Contents**

| 1        | S        | SyncBox Summary                                          | 3 |

|----------|----------|----------------------------------------------------------|---|

|          |          | Command IO Processor:                                    |   |

|          | 1.2      | Sync Generator CPLD:                                     | 3 |

| <u>2</u> | <u>C</u> | Command Summary                                          | 4 |

| 3        | <u>C</u> | Command Communications Set-up.                           | 4 |

| <u>4</u> |          | Command Input Variables                                  |   |

|          | 4.1      | Sync_Length Period Count                                 | 5 |

|          |          | I.1.1 Row_Len period count [default = 64]                |   |

|          |          | 1.1.2 Num_Rows count [default = 41]                      |   |

|          |          | RTS_Mode or FreeRun_Mode [default = FreeRun]             |   |

|          |          | FreeRun_Mode DV period count [default = 47]              |   |

| <u>5</u> |          | SyncBox Status and Error Messages                        |   |

| <u>6</u> |          | SyncBox Outputs                                          |   |

|          |          | MCE Fiber Optic Outputs Manchester Bit Stream Components |   |

|          |          | 5.1.1 25 MHz Clock, Clk25M                               |   |

|          |          | 5.1.2 Address Zero                                       |   |

|          |          | 5.1.3 Data Valid Information                             |   |

|          |          | Data Valid Output To FTS and Polarimeter                 |   |

|          | 6.3      | T T                                                      | 7 |

| _        |          | Front Panel LEDs                                         |   |

| <u>7</u> |          | SyncBox Inputs                                           |   |

|          |          | Commands and Status Serial IO                            |   |

|          |          | Data Valid Input [DV_RTS]                                |   |

| 0        |          | Reset Button                                             |   |

| <u>8</u> |          | Other Box Inputs And Outputs                             |   |

|          |          | MCE Power Supplies Status inputs                         |   |

|          |          | MCE Power Supplies Enable Outputs                        |   |

|          | 8.3      | T T T T T T T T T T T T T T T T T T T                    |   |

| Λ        | 8.4      | 1                                                        |   |

| 9        |          | Jpdating The Command Software                            |   |

| 10       |          | Jpdating The Sync Generation Firmware                    |   |

| 11<br>12 |          | Power And Environmental Specifications.                  |   |

| 12       | <u> </u> | References:                                              | 9 |

## 1 SyncBox Summary

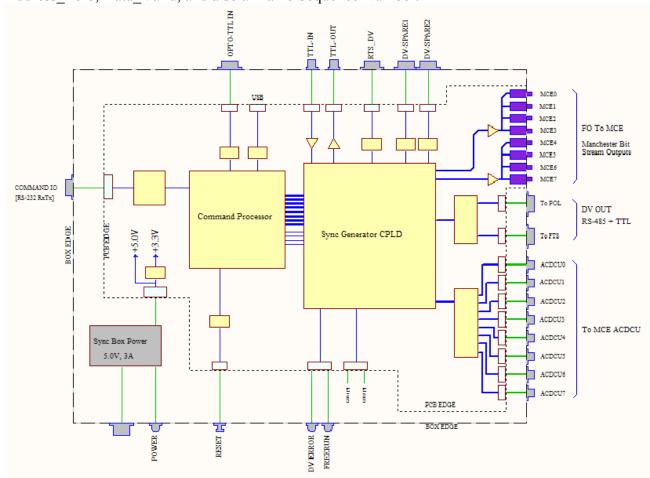

The SyncBox distributes Address Zero and Data Valid information to the eight MCE Clock Cards to synchronise their data collection functions. It is controlled by a Command Processor with connections to a CPLD [all located on the same PCB]. User commands are input to the Command Processor via RS-232. The CPLD generates a serial bit stream which is Manchester encoded with a 25 MHz clock, and contains information for occurrences of Address Zero, Data Valid, and also a Frame Sequence Number.

#### 1.1 Command IO Processor:

Commands are sent to the SyncBox by a 9600 baud RS-232 link to an Atmel AT89C5131A-M, which is a version of the 80C51 single-chip 8-bit microcontroller.

Input command variables are checked by the Command Processor and loaded one byte at a time into the Sync Generator CPLD over programmed IO connections with eight bits for data and an eight bit address.

#### 1.2 Sync Generator CPLD:

Generation and distribution of the Manchester bit-stream, the Data Valid signal, etc., is done by firmware in an Altera MAXII CPLD.

## 2 Command Summary

| h                                                     | Help. List these commands.                |                 |                              |  |  |

|-------------------------------------------------------|-------------------------------------------|-----------------|------------------------------|--|--|

| ?                                                     |                                           |                 |                              |  |  |

| rl n                                                  | set Row_Length to n                       | n = 1  to  4095 |                              |  |  |

| nr n                                                  | Set Num_Rows to n.                        | n = 1  to  63   |                              |  |  |

| rt                                                    | Switch to RTS_Mode.                       |                 |                              |  |  |

| fr n                                                  | Switch to FreeRun_Mode with a count of n. |                 | n = 1  to  4095              |  |  |

| [if n omitted, then use previous n or default value.] |                                           |                 |                              |  |  |

| fn n                                                  | Set Frame Sequence Number counter to n.   |                 | $n = 0 \text{ to } 2^{32}-1$ |  |  |

| go Enable Manchester and Data Valid outputs.          |                                           |                 |                              |  |  |

| st Stop. Disable Manchester and Data Valid outputs.   |                                           |                 |                              |  |  |

| re                                                    | Reset all to defaults.                    |                 |                              |  |  |

| dpa                                                   | Disable all ACDCU power units.            |                 |                              |  |  |

| dpu n                                                 | Disable ACDCU power unit r                | n.              | n = 0 to 7                   |  |  |

| epu n                                                 | Enable ACDCU power unit n                 | ı <b>.</b>      | n = 0 to 7                   |  |  |

| pof                                                   | Get ACDCU_onoff control byte.             |                 |                              |  |  |

| ps                                                    | Get ACDCU status byte.                    |                 |                              |  |  |

#### Notes:

- 1. Row\_Length  $\times$  Num\_Rows must be  $\ge$  250.

- 2. For the SyncBox, Row Length is counted in cycles of 25MHz

# 3 Command Communications Set-up

Sending commands to the SyncBox can be done from a PC running Windows by using HyperTerminal. Start HyperTerminal using the file **Synco-Com.ht**, or set HyperTerminal as follows:

COM Port: 9600 baud, 8bits, no parity, 1 stop bit, no flow control.

Emulation: VT100. Character set ASCII.

Backspace key sends "Ctrl-H, Space, Ctrl-H".

Append line feeds to incoming line ends.

More than one command may be put on a single input command line, up to a maximum of 12 tokens [commands + arguments], and 80 characters. For repeated use this string of commands and arguments could be put into a [one line only] text file.

## 4 Command Input Variables

#### 4.1 Sync Length Period Count

In the Sync Generator CPLD, Row\_Len and Num\_Rows count functions are combined into a single 18 bit counter, but are still settable independently as defined in the next two sub-sections. To allow time for the output of the 5MHz Data\_Valid information, the minimum Sync\_Length permitted will be 250. If (Row\_Len x Num\_Rows) < 250, an error will be reported. The SyncBox counts Sync\_Length in cycles of 25MHz, and it is assumed the Row\_Len value it receives has been scaled appropriately to match the counting done in the MCE.

#### 4.1.1 Row Len period count [default = 64]

Row Len is settable from 1 to 4094, and counts cycles of Clk 25M.

#### 4.1.2 Num Rows count [default = 41]

Num\_Rows is settable from 1 to 63, and counts cycles of Row\_Len. Output is Addr\_Zero [The sync box does not take into account MCE start rows other than zero.]

### 4.2 RTS Mode or FreeRun Mode [default = FreeRun]

The commands rt and fr nnnn switch between RTS\_Mode and FreeRun\_Mode. In FreeRun\_Mode DV\_RTS is ignored.

### 4.3 FreeRun Mode DV period count [default = 47]

When in FreeRun\_Mode the sync box generates it own Data\_Valid by down-counting occurrences of Addr\_Zero from a command settable number between 1 and 4095. When the count goes to zero, it outputs a FreeRun\_DV, and re-loads to repeat the count. If N < 1 an error will be reported. If N is omitted, the default or previous value is used. If the sync box is in RTS\_Mode, FreeRun\_DV output is ignored.

## 5 SyncBox Status and Error Messages

#### **Status Output Format:**

Mancho\_Enable = ON DV\_Mode = FreeRun\_DV FRUN\_COUNT = 47 Row\_Len = 64 Num\_Row = 41 ACDCU\_onoff = 0X00

#### **Some Error Messages:**

```

Synco> xx WHAT? "xx" // Unreconized command.

Synco> rl 9999 TOO BIG "9999" // Command parameter too large.

Synco> rl 0 TOO SMALL "0" // or too small.

Synco> rl xx WHAT? "xx" // could not parse the parameter value.

```

## **6** SyncBox Outputs

### 6.1 MCE Fiber Optic Outputs Manchester Bit Stream Components

There are eight FO outputs which will connect to the MCE Clock Cards. The FO outputs are divided into two groups of four each, for a possible future dual-rate operating mode.

#### 6.1.1 25 MHz Clock, Clk25M

This is the Manchester bit-stream clock. It is always output as a stream of ones, except as specified below.

#### 6.1.2 Address Zero

Occurrences of **Addr\_Zero** are encoded into the Manchester bit-stream as a single binary '0'. It is output every time the **Sync\_Length** count completes, where Sync\_Length = **Row\_Length** × **Num Rows**, and counts cycles of **Clk25M**.

#### 6.1.3 Data Valid Information

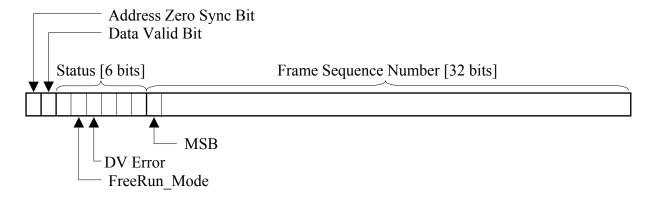

This sequence contains Address Zero, Data\_Valid, Status Bits, and a Frame Sequence Number. It is output when **Addr\_Zero** occurs, and a **DV\_RTS** [or a **FreeRun\_DV** if in FreeRun\_Mode] has occurred during the preceding Sync\_Length count. Addr\_Zero and DV are encoded into the Manchester bit-stream as binary '00'. They are followed by a 6 bit status word, and then a 32 bit Frame Sequence Number count, for a total of 40 bits.

If two or more DV have occurred during a Sync\_Length count the **DV\_Error** bit will be set [this can only occur when in RTS Mode].

## 6.2 Data Valid Output To FTS and Polarimeter

This is a buffered version of DV\_RTS, or FreeRun\_DV if the SyncBox is in FreeRun\_Mode. The DV output for FTS or Polarimeter use will be about 1µsec wide, active low, and is delayed to occur at the next Addr\_Zero, when the manchester bit stream Data Valid and Frame Sequence Number are output. Both outputs have an RS485 and a TTL output.

## 6.3 Spare RS-485 / 5MHz NRZ Outputs

There are two spare RS-485 only outputs, which are used for a 5MHz NRZ and clock version of the Data Valid information. DV\_Spare1 has the 5MHz clock output, and DV\_Spare 2 has the NRZ DV information stream.

NOTE: the 5Mhz output contains only the DV info stream, but not the occurrences of Addr\_Zero between DVs

#### **6.4** Front Panel LEDs

#### FreeRun Mode

This LED is on when the SyncBox is in FreeRun Mode

#### **DV** Error

When two or more DV occur during a Sync\_Length count the DV\_Error LED will be turned on [this can only occur when in RTS\_Mode]. The LED is turned off at the next Addr\_Zero.

## 7 SyncBox Inputs

#### 7.1 Commands and Status Serial IO

One RS-232 IO connection. See Command Communications Set-up.

## 7.2 Data Valid Input [DV\_RTS]

Data Valid RS-485 input from RTS. Any falling edge will be taken as a DV signal.

#### 7.3 Reset Button

Resets all control states and parameters to the default startup values.

## 8 Other Box Inputs And Outputs

## 8.1 MCE Power Supplies Status inputs

Eight inputs driven from optocouplers in the MCE ACDCUs give enabled / disabled information. This can be checked with the 'ps' command, which will reply with an ASCII hex encoded version of the ACDCU status byte.

Synco> ps

ACDCU Status = 0X7B

### **8.2** MCE Power Supplies Enable Outputs

Eight outputs to drive enabling optocouplers in the MCE ACDCUs.

## 8.3 Spare Opto-TTL Input

A One bit optocoupler isolated input to the Command Processor is available. [This input is ignored in this version.]

### 8.4 Spare TTL-Out and TTL-In

These connect to the Sync Generator Module. In this version, TTL-Out will get a NRZ version of the 25MHz synchronizer bit stream information. TTL-In is not used.

## 9 Updating The Command Softwware

If you want to modify the command software you will need the Keil uVision3 IDE. See the Keil website <a href="https://www.keil.com">www.keil.com</a> for details.

Loading the uVision3 output hex file into the AT89C5131A-M is done using the USB port and the Atmel Flip utility (FLexible In-system Programmer), which can be downloaded from the Atmel website, <a href="www.atmel.com">www.atmel.com</a>. [Flip is a Java application, so you will also need the Java Run-time Environment]

On the SyncBox PCB [with power applied]:

To reprogram BLJB or to get the bootloader to restart so that you can download new code, the PSEN and RESET switches must be held down while the USB connector is inserted. Reset is then released followed by PSEN.

### In Flip:

Click on the Target Device icon and select AT89C5131.

Make sure that BLJB is unchecked so that the user program will always start after a reset.

Get the hex file. [File -> Load HEX File]

Click on the USB icon and open the UBS connection.

Click on the Run button, and wait while the programming sequence completes.

Click on the Start Application button.

## 10 **Updating The Sync Generation Firmware**

## 11 Power And Environmental Specifications

- Power supply, Lamda RWS15A, input voltage range 85 to 265VAC, 47 to 440Hz.

- Power inlet filter, Corcom 1EEJ1, is rated 1A, 250VAC[max], 50/60Hz

- Operating temperature range 0 to +30 C or better.

- Time base stable to  $\pm$  50 PPM or better over temperature range.

# 12 References:

- [1] Timing and response to Data Valid Pulses [dv\_timing.pdf] M.Halpern 2005-08-11

- [2] MCE\_Interfaces\_SCUBA2\_Rev2.pdf

- [x] MCE User's Manual

- [x] Atmel 89C5131AM data sheet

- [x] Atmel 8051 Microcontrollers Hardware Manual

- [x] Altera MAXII Device Handbook